FT-J2 Free Topology Transceiver up date 2025.4.15

FT-J2 Free Topology Transceiver

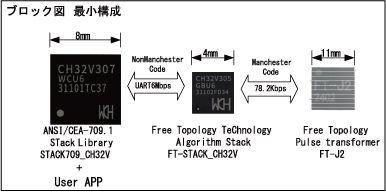

The FT-J2 Free Topology Transceiver is a transceiver compliant with ANSI/CEA-709.3+R2015.

Combining the ANSI/CEA-709.1-B (EN14908.1) protocol stack with the FT-J2 transceiver,

it is a pulse transformer that can be connected to the FT-10 Free Topology Network.

The FT-J2 is a pulse transformer that can be connected to the FT-709MW, EIA709MW, and FT-5000.

First, let me introduce the FT-J2 free topology transceiver.

FT-J2 catalog(EN)